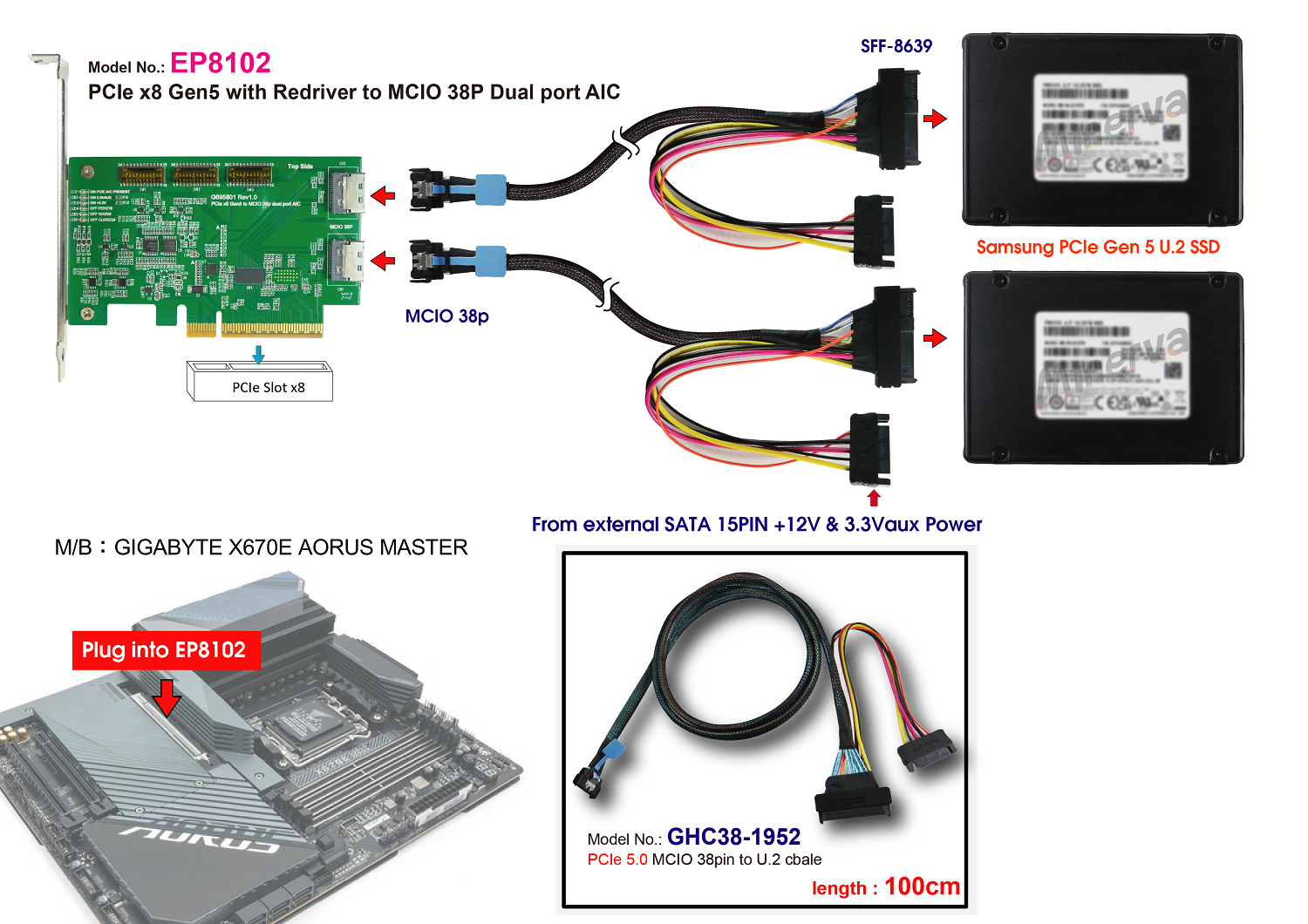

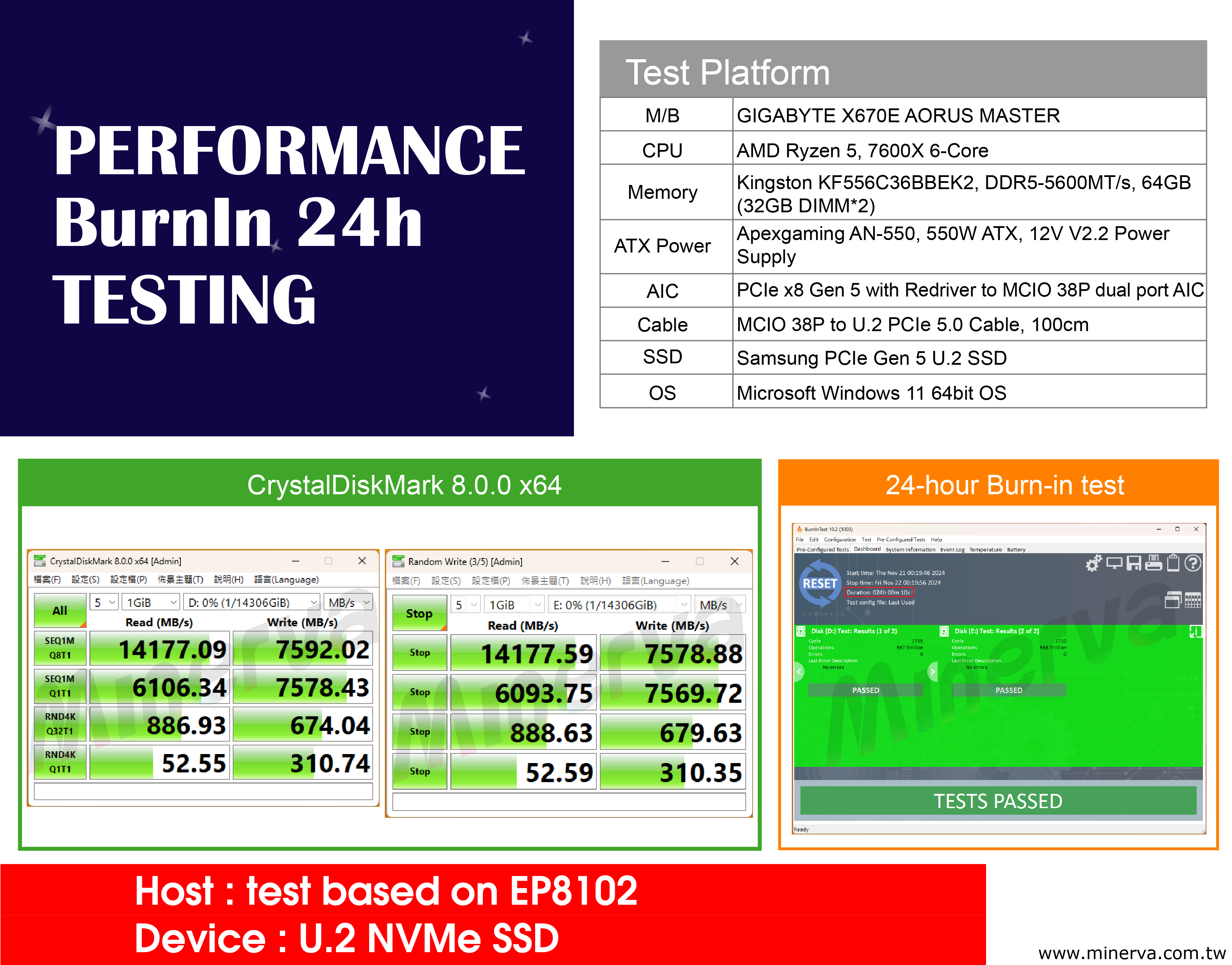

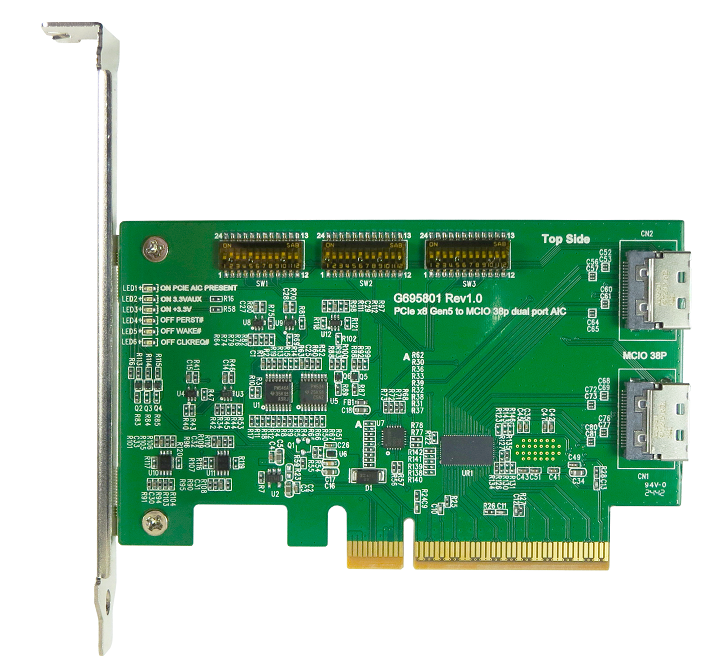

- MCIO 38P (SFF-TA-1016) dual port to PCIe x8 Gen 5 convert

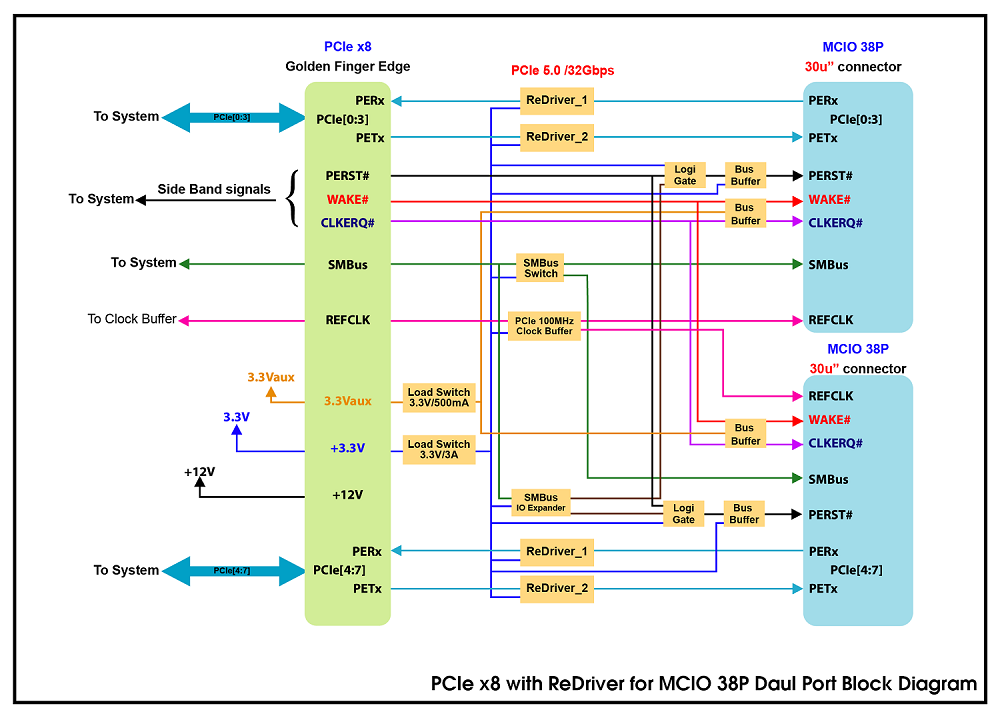

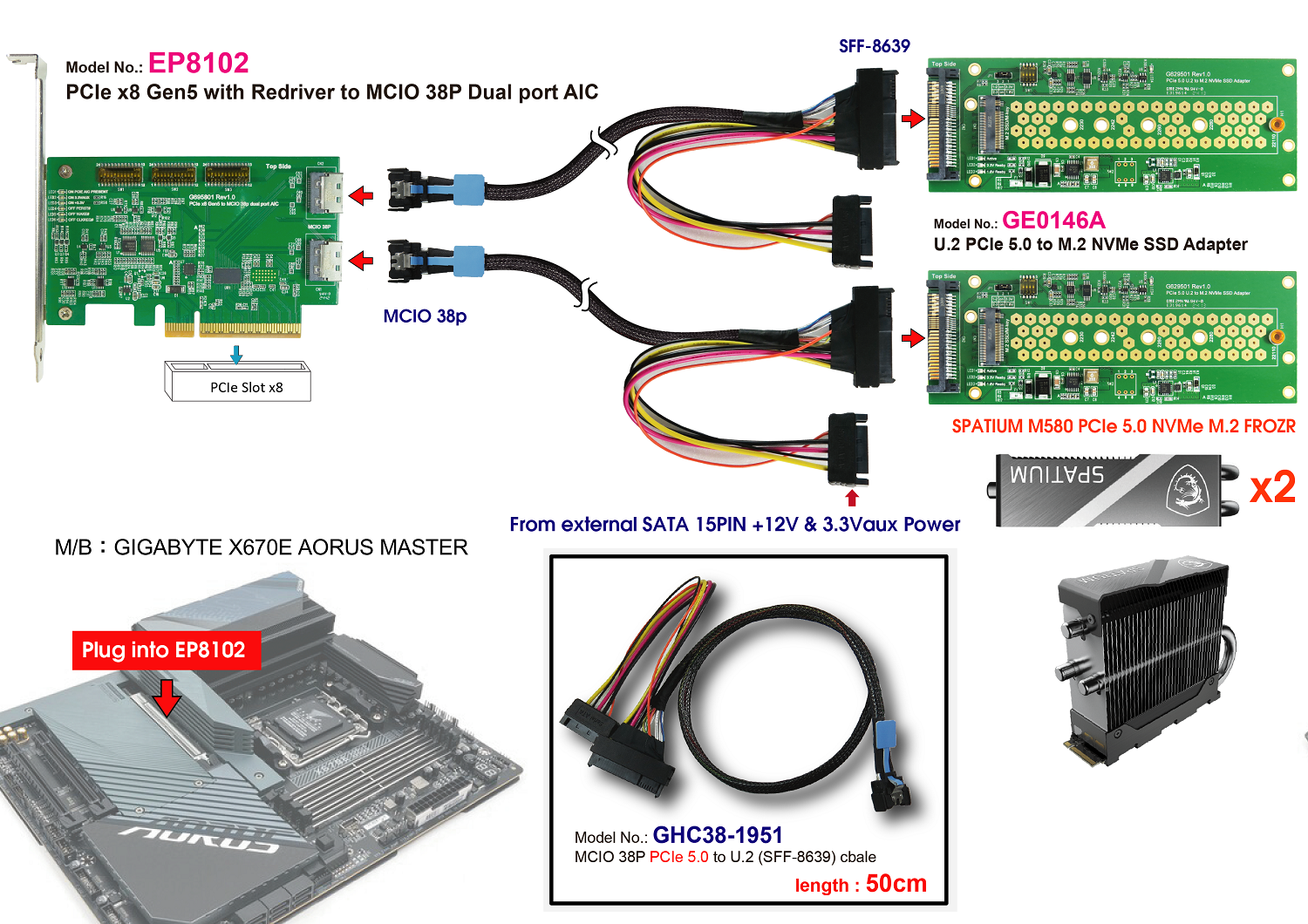

- Built-in MCIO 38P (SFF-TA-1016) connector dual port

- Built-in ReDriver to extend PCIe 5.0 8 Lanes signals data link width reach.

- Built-in PCIe 100MHz Clock buffer(Address: 0x6C/7 bits), default Zout=100 ohm to drive longer trace length and longer cable length.

- Built-in PCIe SMBus Switch(Address:0x70/7 bits) 4-channel with Reset Function for MCIO 38P (SFF-TA-1016) and PCIe 100MHz Clock buffer SMBus control

- Built-in SMBus I/O Expander(Address: 0x20/7 bits) for OOB(out of band) management to remote MCIO 38P dual port Reset signals

- Built-in PERST# Bus Buffer Gate to be used over longer trace lengths and longer cable length.

- Built-in WAKE# Bus Buffer Gate to be used over longer trace lengths and longer cable length.

- Built-in CLKREQ# Bus Buffer Gate to be used over longer trace lengths and longer over cable length.

- LED1 Green ON indicates AIC PRSNT#

- LED2 Green ON indicates 3.3VAUX ready

- LED3 Green ON indicates 3.3Vready

- LED4 Green OFF indicates PERST# Normal (Function intentionally inverted)

- LED5 Green OFF indicates WAKE# Normal (Function intentionally inverted)

- LED6 Green OFF indicates CLKREQ# Normal (Function intentionally inverted)