Datasheet

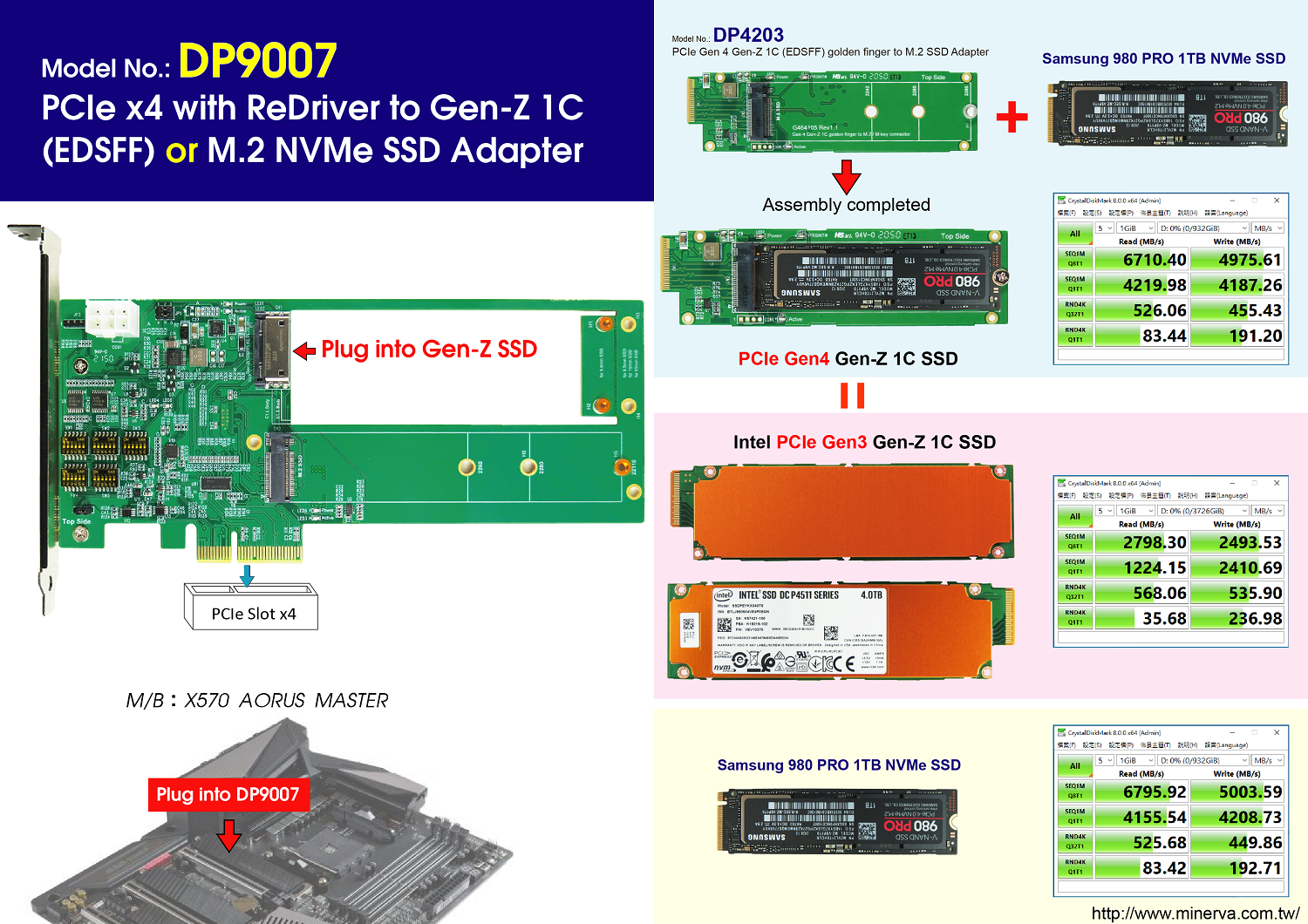

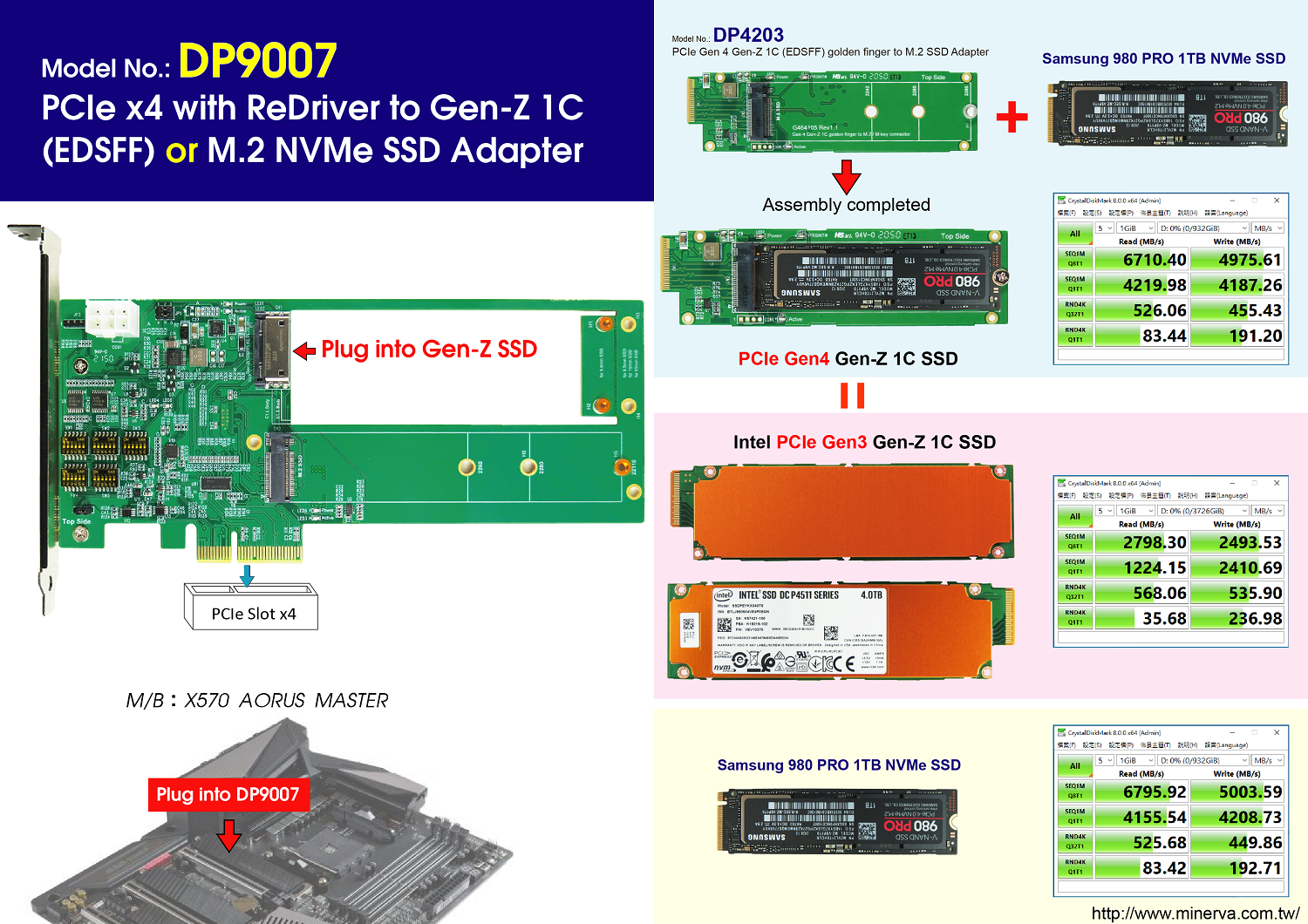

Test report for DP4203+M.2 NVMe SSD

Test report for M.2 NVMe SSD

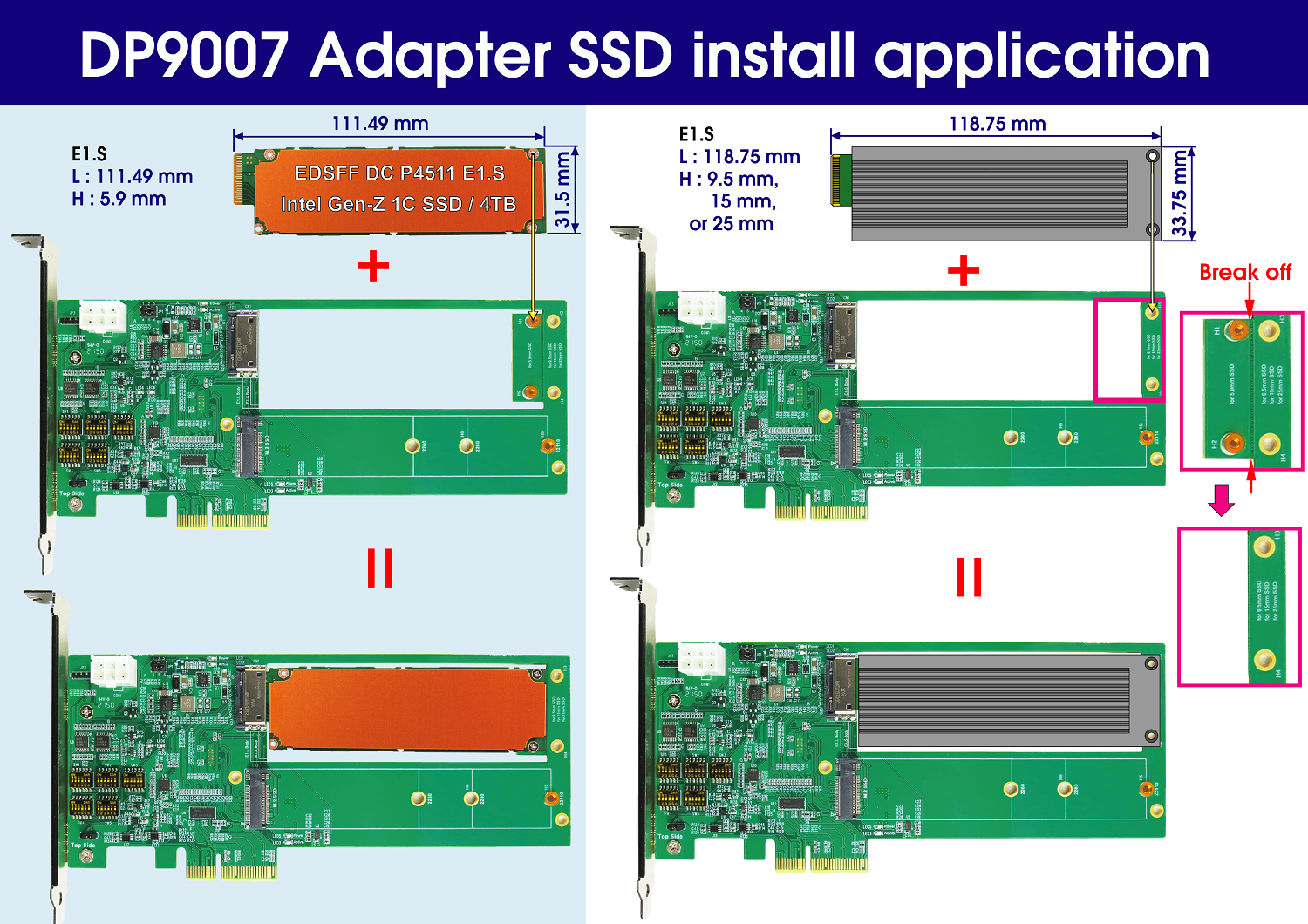

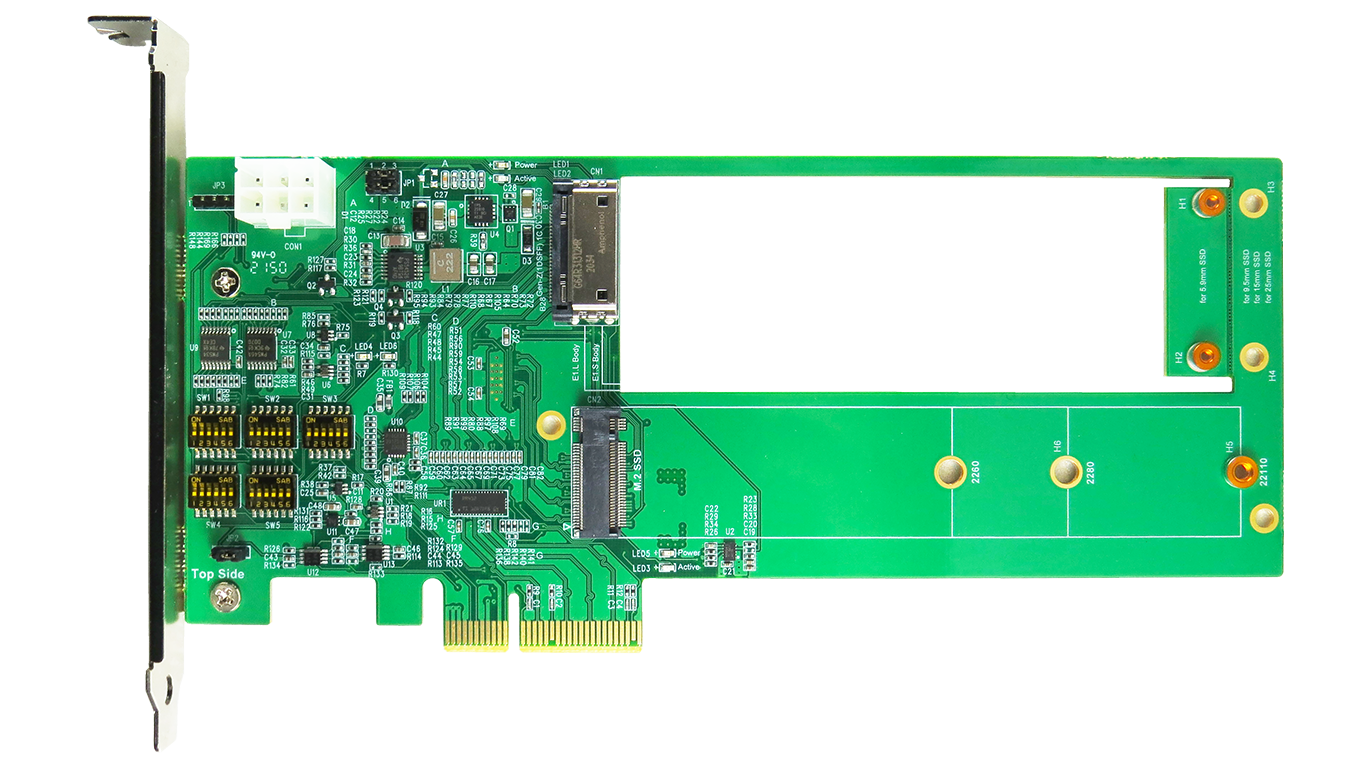

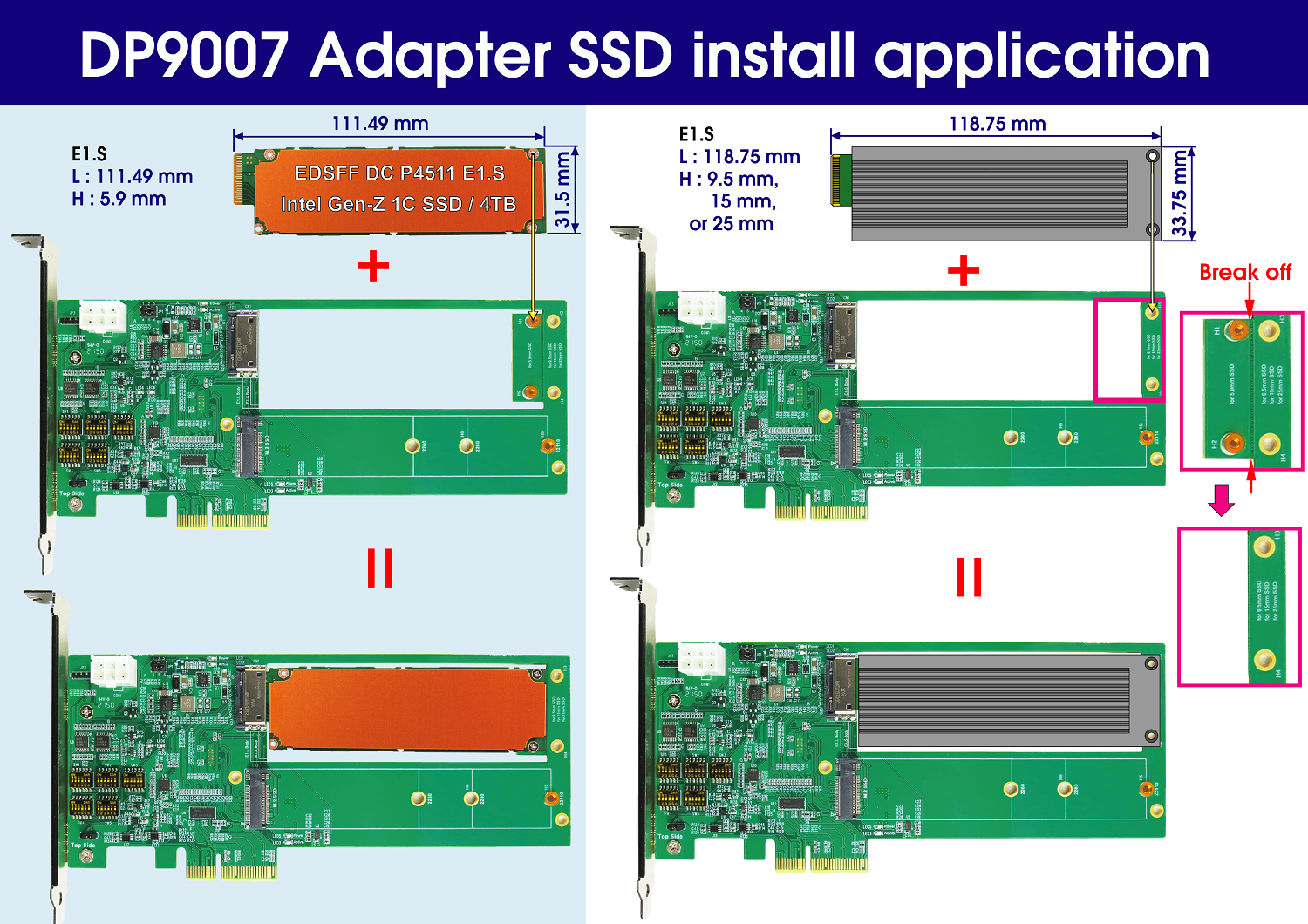

DP9007-2D drawing

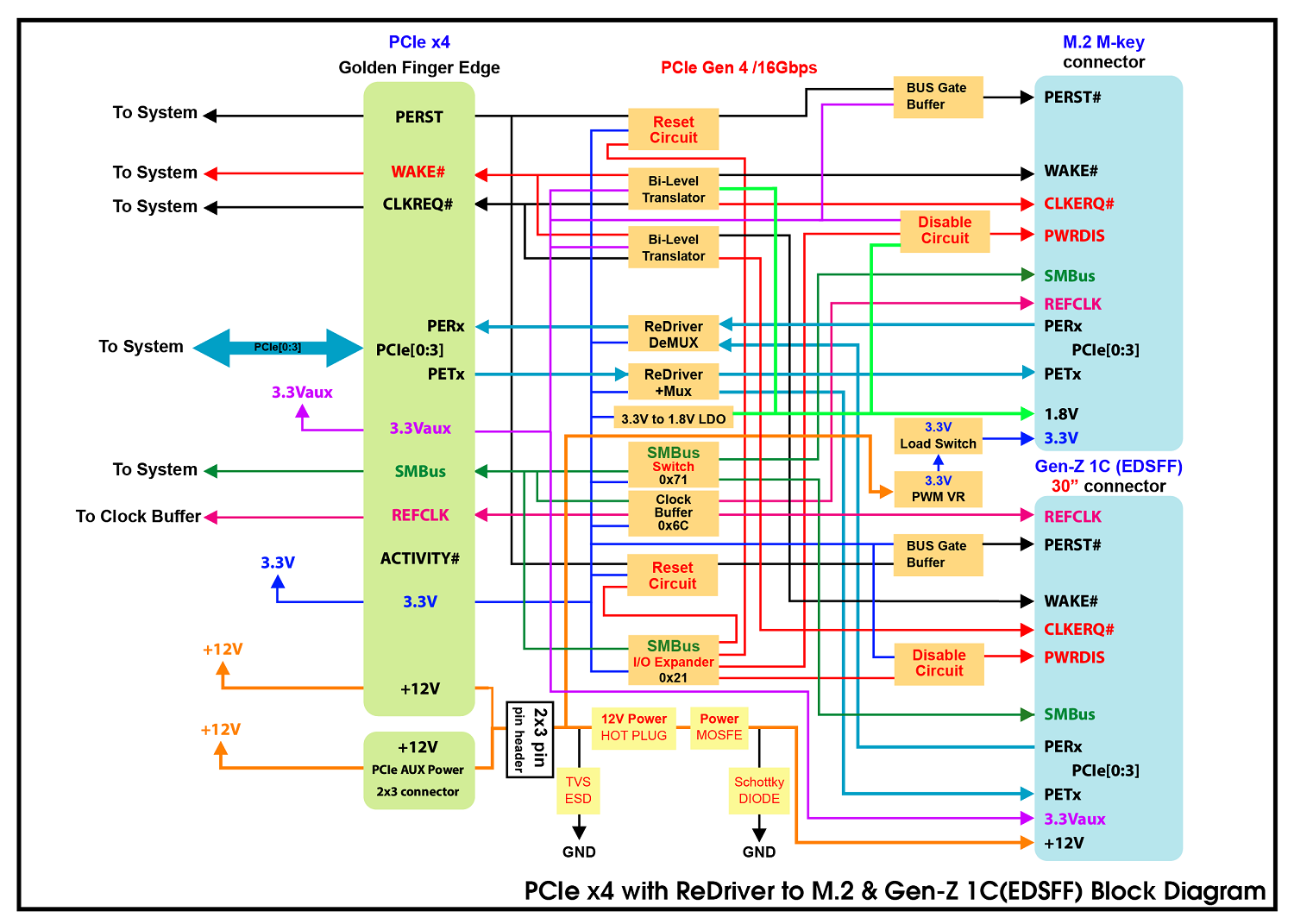

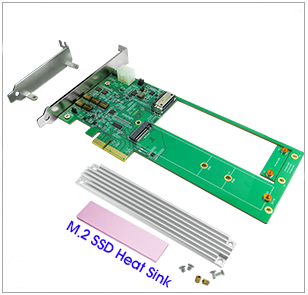

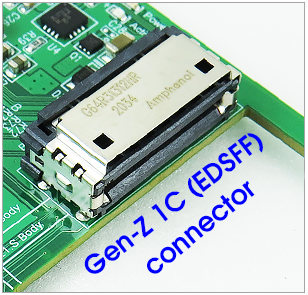

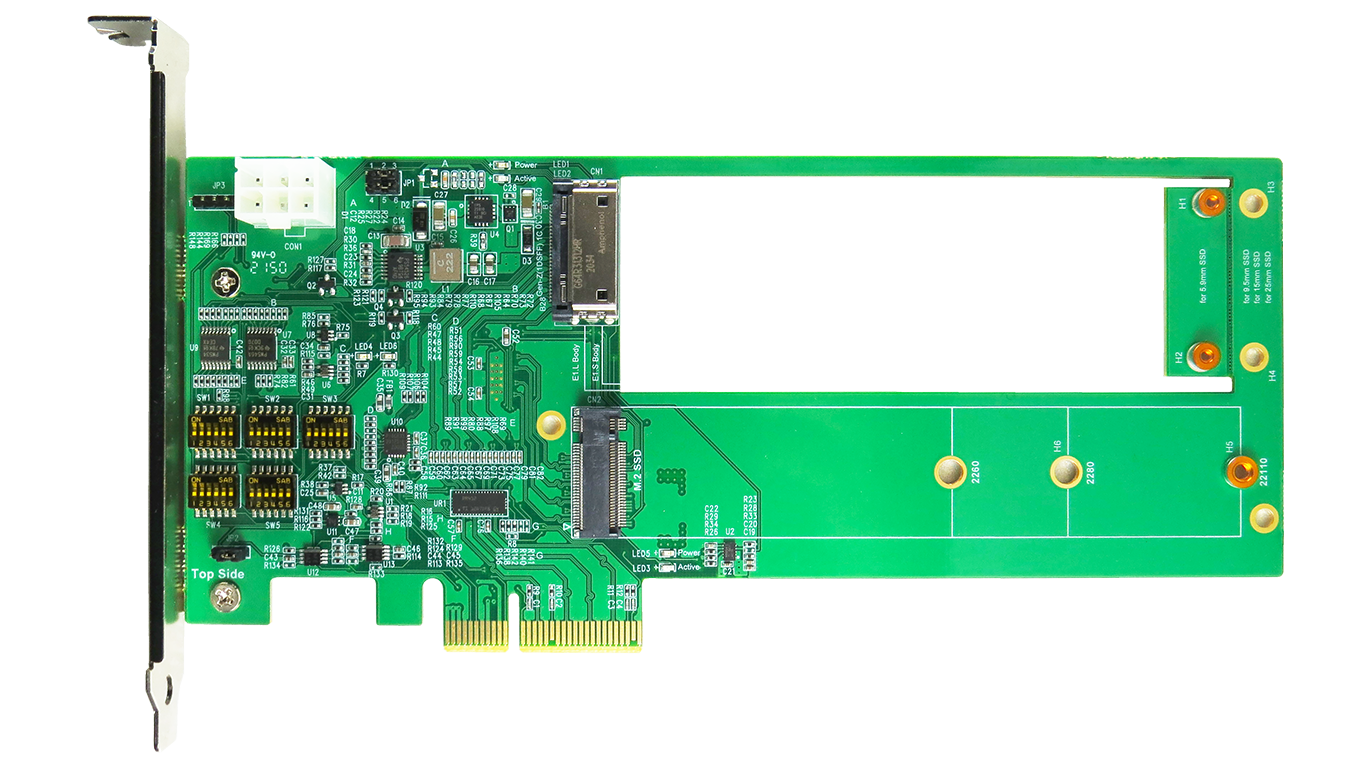

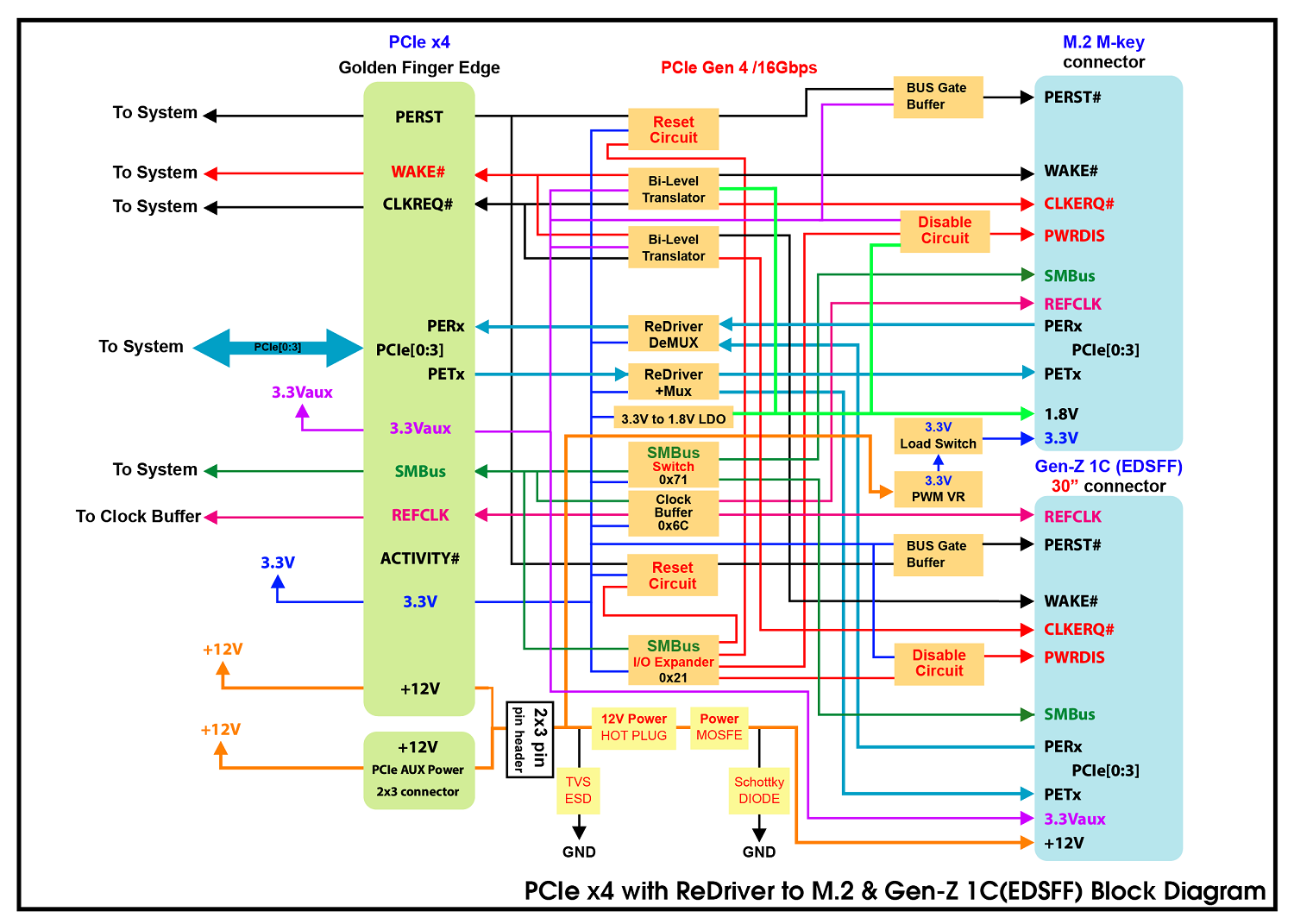

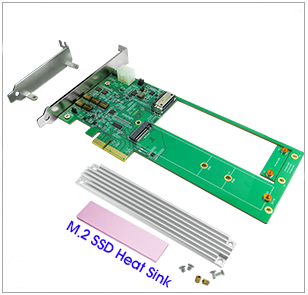

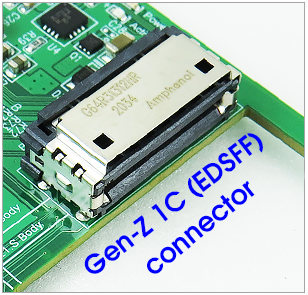

- Gen-Z 1C (EDSFF) to PCI Express 4.0 x4 convert

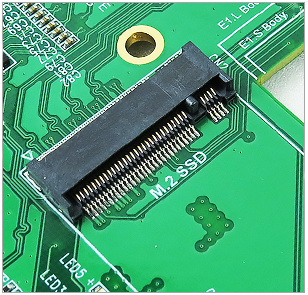

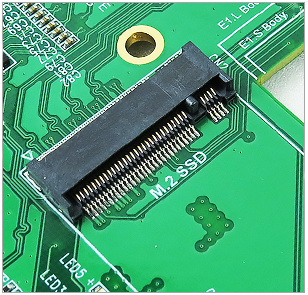

- Gen-Z 1C (EDSFF) or M.2 M-key to PCIe 4.0 x4 convert, two choose one

- Built- in EDSFF 1C with latch connector

- Built- in M.2 M-key connector

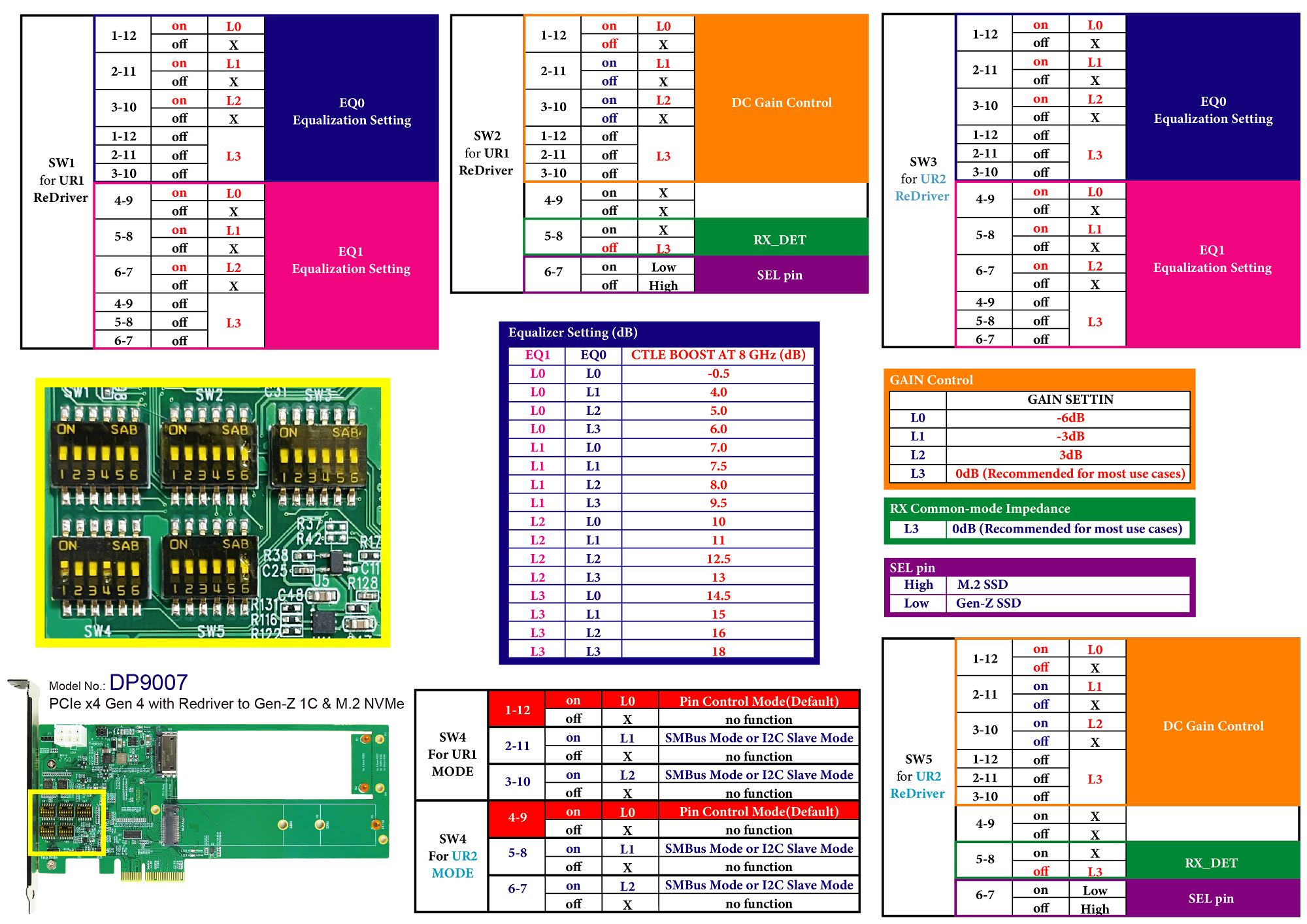

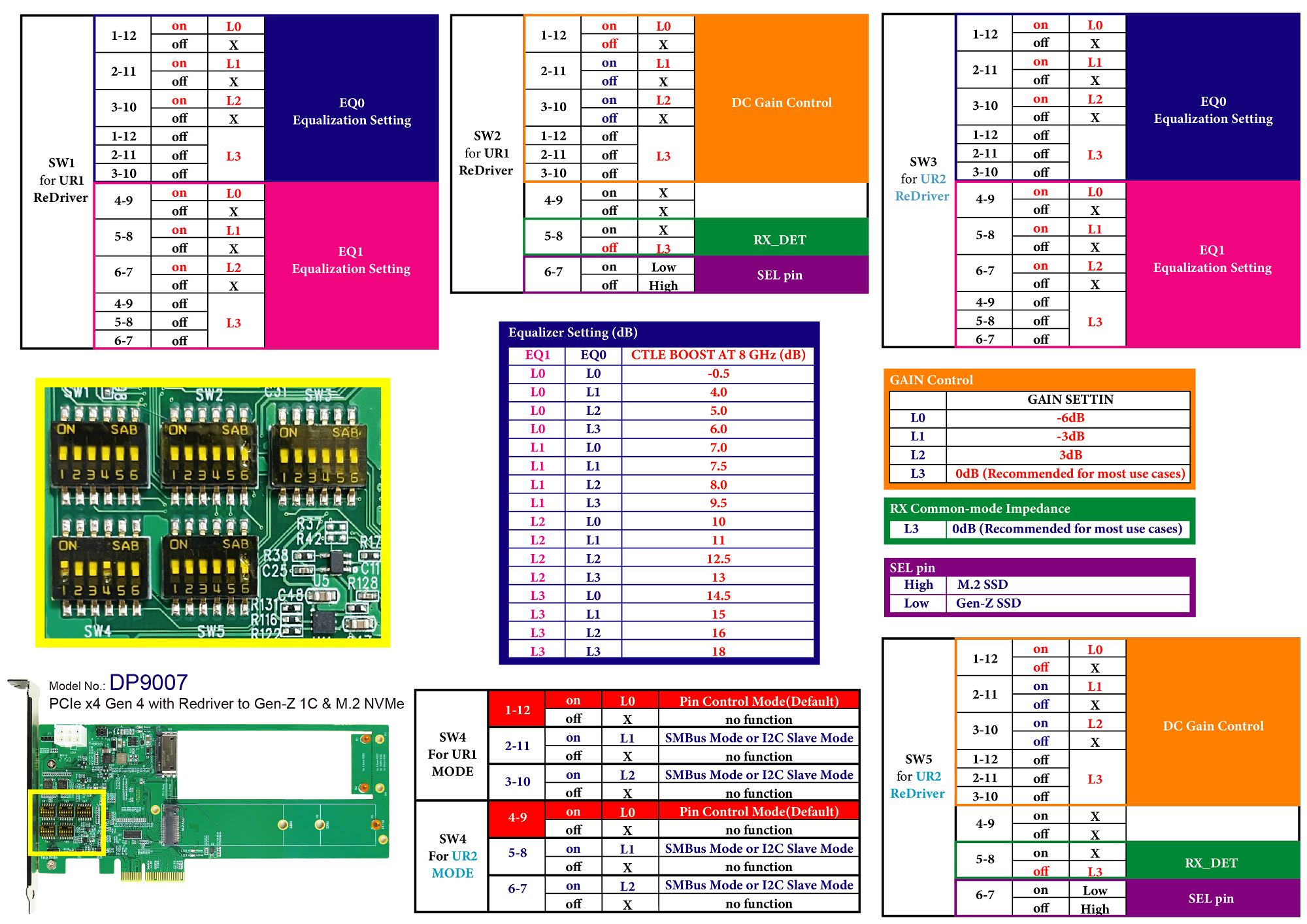

- Built- in PCIe ReDriver to extend PCIe Gen4, 16GT/s differential pair signals

- The controller with its CTLE set to the maximum gain to 17 dB boost

- Built- in PCIe 100MHz Clock buffer to drive longer trace lengths and longer cable with SMBus

(Address: 0x6C/7 bits) for BMC & IPMI control

- Built- in SMBus Switch with Reset Function(Address: 0x71/7 bits) for Gen-Z 1C & M.2 SMBus

- Built- in SMBus I/O Expander(Address: 0x21/7 bits)

- For EDSFF PWRDIS, SMBRST# control

- For M.2 PWRDIS control

- PCIe PERST# for OOB(Out Of Band) management to remote Gen-Z & M.2 Reset

- Control Gen-Z 12V enable or disable

- Control M.2 3.3V enable or disable

- Built- in PCIe PERST# Bus Buffer Gate to be used over longer trace lengths and over longer cable

- Built- in PCIe WAKE# Bus Buffer Gate to be used over longer trace lengths and over longer cable

- Built- in PCIe CLKREQ# Bus Buffer Gate to be used over longer trace lengths and longer over cable